今回は半導体材料のなかでも、今アツい後工程材料を解説します。

生成AIバブルを背景に注目が集まる後工程技術ですが、実は日本の化学メーカーが強みを持つ部分でもあります。

最先端技術から関連する化学メーカーまで紹介していきます。

それではどうぞ。

半導体材料とは

まずは半導体についてのおさらいから。

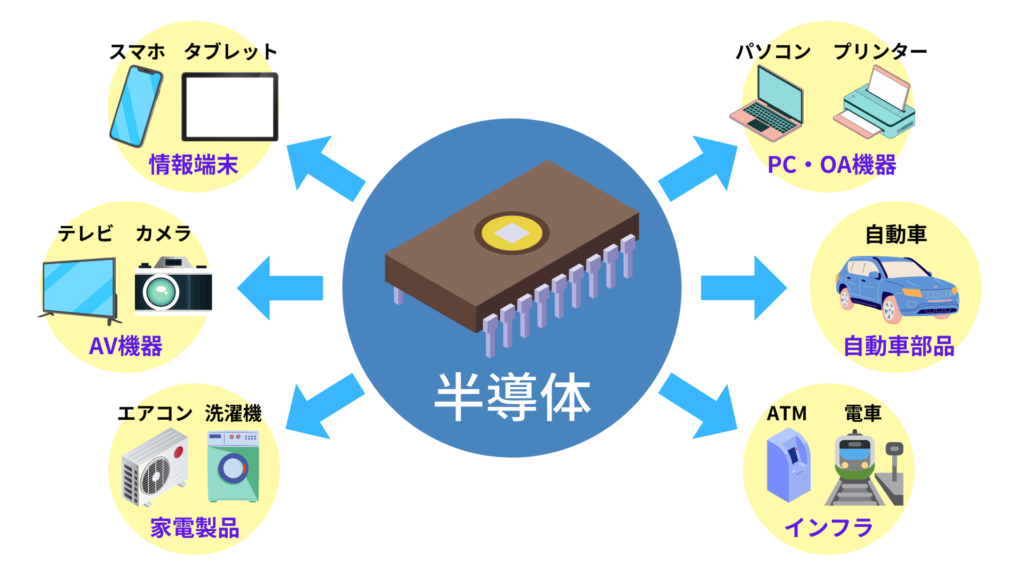

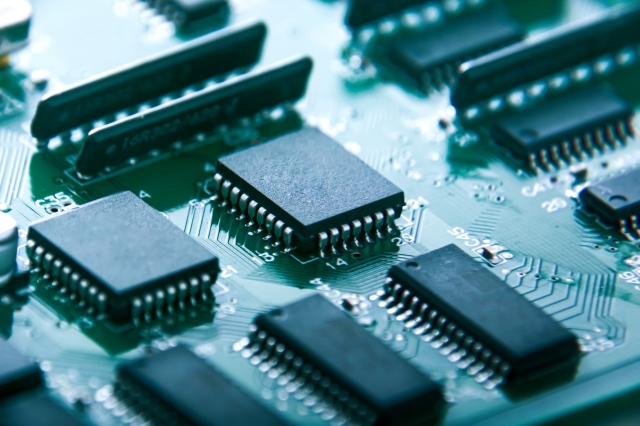

半導体はスマホやパソコン、またデータセンター、ほかにもさまざまな電子デバイスの頭脳として用いられています。

出典 Semi journal

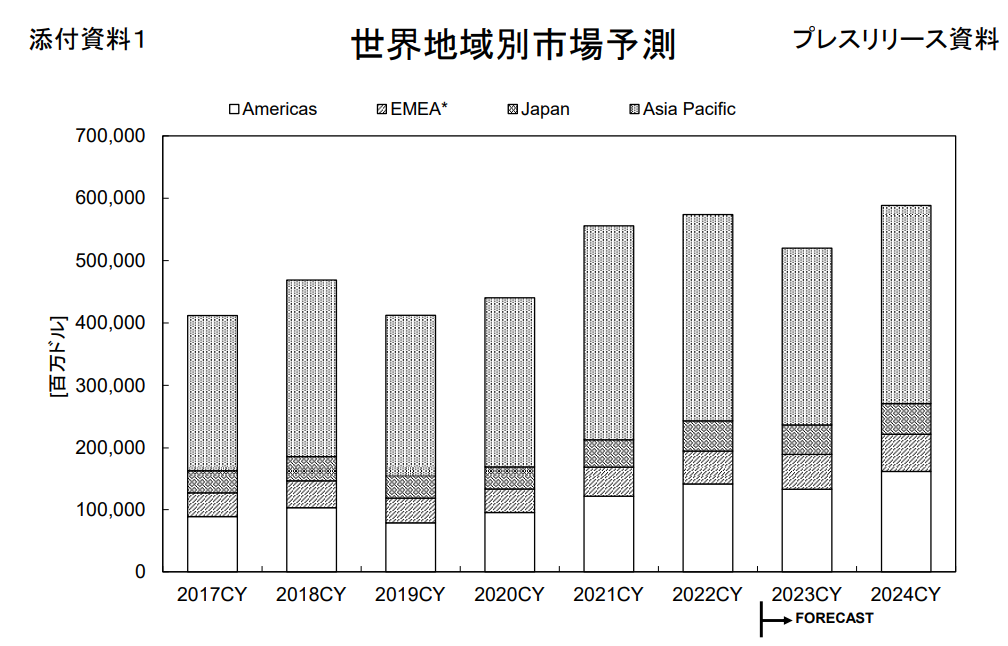

今後も生成AIや自動運転、メタバースなど、あらゆる産業の発展が半導体の進化にかかっており、

将来的に半導体産業は自動車産業を超えるともされる、とんでもなく巨大な成長市場です。

そんな情報化社会の核であり、株式市場でも一大ムーブメントを巻き起こした無敵のアイドル半導体ですが、

その製造では米Intel、韓サムスン、また台TSMCなど海外企業が大手、残念ながら日系メーカーのシェアはさほど高くありません。

ただ半導体の製造プロセスには多くの化学製品が用いられ、そういった半導体材料に関しては日系の化学メーカーが高いシェアを誇っているのです。

過去日本でも半導体産業が盛んだった時代に、半導体材料も礎を築いたことや、

半導体プロセスに求められる繊細さが、手先が器用で根気強い日本人技術者とマッチしていた、など要因はいろいろあるようですが、

日系企業にとって半導体材料はまさに、コアコンピタンスを発揮できる分野なのです。

ゆえに株式市場でも半導体材料を手掛ける化学メーカーは注目が集まっており、企業側も経営戦略の柱の一つに据えているわけですね。

後工程とは

それでは今回のテーマ、今が激アツとされる後工程材料について。

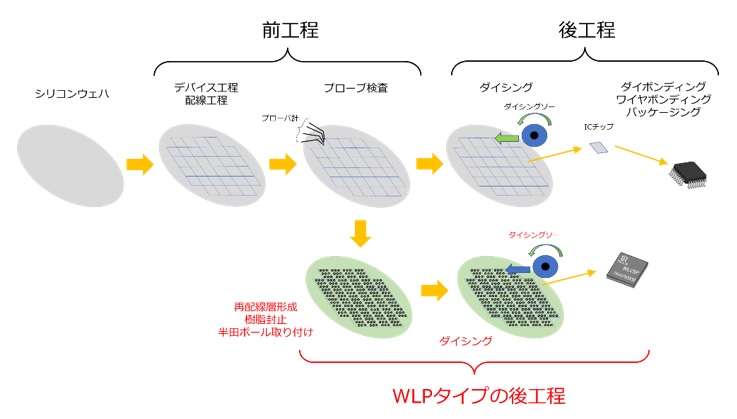

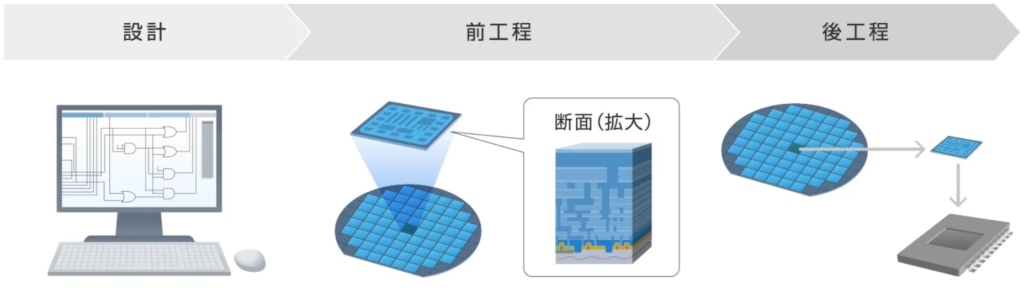

そもそも後工程ってなんや、という話ですが、半導体の製造プロセスは、大きく前工程と後工程に分けられます。

前工程はシリコンウエハに微細な回路を描く工程で、対して後工程はウエハからチップを切り出してパッケージ化する工程です。

半導体を電子機器の頭脳と表現しましたが、前工程が脳みそ(チップ)を作っているとすれば、

後工程は脳みそを神経とつなぎ、外部環境から脳みそを守るために頭蓋骨に入れる工程(パッケージング)と言えます。

この頭脳となった半導体パッケージをマザーボードに実装することで、見覚えのある回路基板になるわけですね。

ではなぜ今この後工程がアツいのか、その前に後工程について、プロセスと材料メーカーを簡単に紹介していきます。

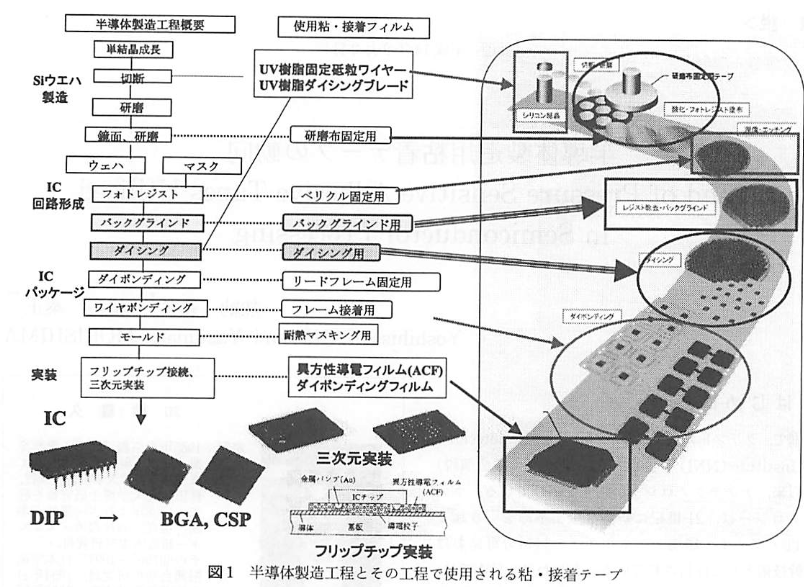

バックグラインド・ダイシング

後工程にもいくつかの段階があるのですが、まず前工程で回路を形成したウエハーを摩擦でゴリゴリで削って薄くしたり、

ピザカッターのようなものでカットして、チップとして切り出す工程があります。

(菅製作所HPより)

このダイシング装置では、半導体装置メーカーのディスコが有名ですね。

ただウエハーが薄くなると脆くなり、割れたり、欠けたり、反りも無視できなくなってきますので、

回路を衝撃や汚れから守る目的で、半導体製造工程用テープが用いられます。

工程ごとにいろいろなテープが用いられますが、総合化学では三井化学がゴリゴリ削る工程を中心にイクロステープを、

また裏面保護に用いられるLCテープでは、粘着剤メーカーであるリンテックの独壇場となります。

リンテックはテープとテープ貼り付け装置をセットで提供している点が強みの一つですね。

ワイヤーボンディング・ダイボンディング

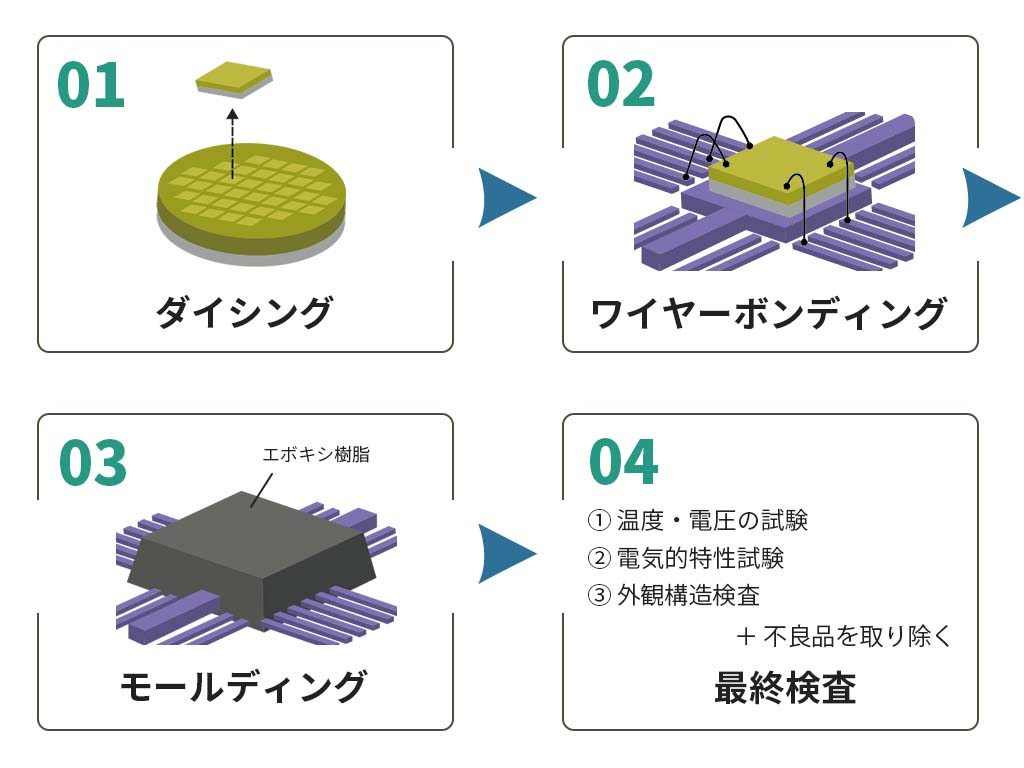

こうしてなんやかんやで切り出したチップを、今度はパッケージしていくことになります。

まずは電気的に接続するため、チップを基板の上にのせたり、リードフレームやワイヤ、またバンプでつないでいきます。

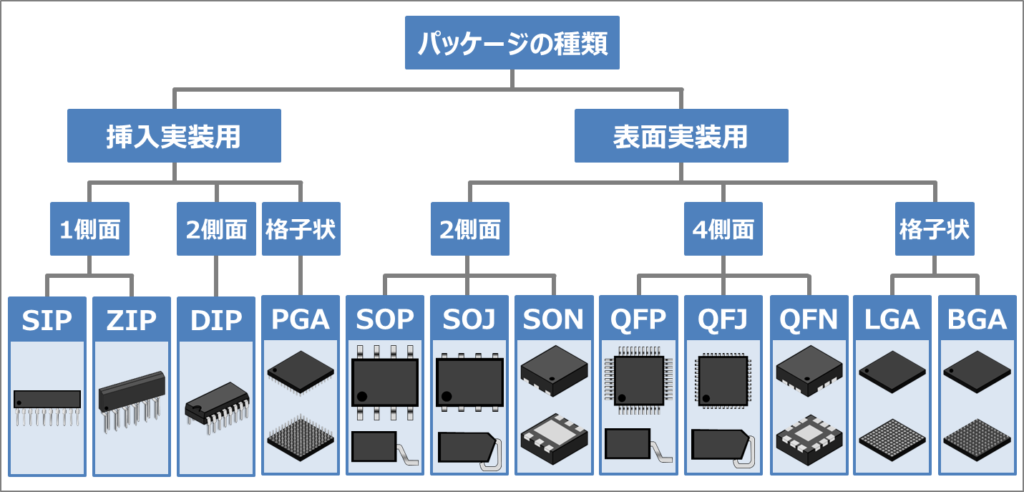

ただ後工程で作られる半導体パッケージはあまりにも種類が多く、なんなら一万種類以上あるとさえ言われており、種類によってプロセスや材料はまた変わってきます。

例えばスマートフォンのAPなどには薄型のFC-CSPが、CPUやGPUには厚型のFC-BGAが使用されます。

そしてFC-CSP基板材料では三菱ガス化学がトップメーカー、対してFC-BGA基板材料ではレゾナックと味の素ファインテクノがデファクトスタンダードを握ります。

またWLPと呼ばれるタイプでは、ウエハ上で再配線を行い、パッケージまで行った後にカットされます。

種類によって材料メーカーの住みわけも変わってくるため、後工程材料の理解を難しくしている要因だったりしますね。

モールディング

最後にチップを外部の水分やイオン、光などから保護するために樹脂でがちがちに固める工程があります。

こうして半導体は見慣れた黒いあれになるわけですが、黒いあれのもとは封止材と呼ばれます。

封止材では住友ベークライトが世界首位で市場の4割、2番手のレゾナックが市場の2割を占めているとされ、両社最大市場の中国で設備増強を進めています。

また封止材は基本的にはエポキシ樹脂とフィラー材料などの混ぜ物ですが、その原料メーカーも日系メーカーが提供していたりしますね。

パッケージの種類は多い

ざっくりと後工程について解説してきましたが、最終的にはパッケージに収められた状態で、電気特性などの検査が行われます。

さまざまな材料が出てきましたが、テープのような製造工程で使われるものと、電気的な接続を行う金属や基板、チップを保護する封止材といったパッケージに関与する材料があるわけですね。

そして各材料で日系メーカーが高いシェアを誇り、住友ベークライトなどは、株価を堅調に上げていたりします。

なぜ後工程がアツいのか

続いては、いま後工程に注目が集まる理由について。

今でこそ注目の的となっている後工程ですが、これまでの半導体プロセスの花形は前工程、後工程は実は脇役のような立場でした。

というのも半導体は回路が微細化するほど性能が向上するため、前工程の微細加工技術が突き詰められ、

前工程に用いられるフォトレジストや露光光源などの進化に注目されてきたのです。

ゆえに加工や検査が主の後工程は重要度が相対的に低く、利益率も高くない傾向にありました。

これはメーカーにおける研究と品質管理のような関係で、日の目を見る機会が少なかった後工程ですが、

今二つの要因が起爆剤となり、注目が集まっているのです。

従来技術は限界

一つは、進化を支えた微細化も限界を迎えている点。

というのもムーアの法則に沿って進んでいた前工程による性能向上も陰りが見える中、チップの大型化による歩留まりの悪化も課題となっていました。

不良を含む確率も上がるため、歩留まりは悪化する。(出所)

そのようななか新たな差異化領域として、後工程でのパッケージング化技術による性能向上が頭角を現してきたのです。

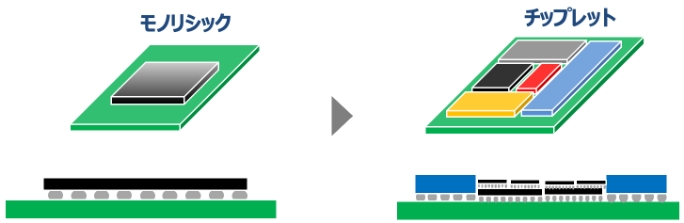

例えばチップレット技術などが挙げられ、従来の単一チップに集積していた大規模な回路ではなく、

機能をばらした複数のチップをつなぎ合わせて大規模化し、一つのパッケージに収めるというものです。

ポケモンでいえば、従来の単一チップがミュウツー一体で無双するスタイル、対してチップレットは複数のポケモンで戦力補完をするイメージでしょうか。

チップレットは歩留まり改善やチップ同士の組み合わせによる高性能化といった様々な利点がありますが、頭脳の例で言えば、一つの頭蓋骨に二つの脳みそを入れるようなもので、その実現には、後工程におけるパッケージング時術の高度化が不可欠となっているわけですね。

生成AIバブル

このように半導体の進化もちょうど転換点を迎え、パッケージング技術を中心とした新たなロードマップが想定される中で、

さらに二段階目のロケットエンジンとしてブーストをかけたのが、生成AIの登場です。

生成AIについての説明は過去記事に譲りますが、

最近でも米マイクロソフトがクラウドではなく端末でAIを動かす、エッジAIのパソコンを公開、

AppleもエッジAIを実現する独自の生成AIを公表するなど、IT各社の開発が加速しています。

先端半導体というのは、主用途であるスマホやPCがその需要に影響を与えているのですが、

今はスマホやPCに生成AIの波がきており、ゆえにAI半導体への期待値も高まっている状況なのです。

そして、膨大なデータ処理が求められるAI半導体には、先端のパッケージ技術である三次元実装が採用されています。

三次元実装の詳細は後ほど解説しますが、生成AIにとってパッケージングの技術革新はもはや欠かせない存在、後工程におけるパッケージング技術の重要さを象徴していますね。

バブルもあるけど、太い流れ

このように中長期的な半導体技術トレンドの変化に、AIバブルが重なり、後工程のパッケージング技術への注目度は過去最高潮、関連銘柄の株価はロケットのごとく突き抜けています。

ただ、半導体業界というのは昔から浮き沈みのある市場であり、AI半導体もメーカーが在庫を多く積み上げた結果、一時的に成長が鈍化する可能性はあります。

生成AIの過熱感には注意が必要ということはお伝えしておきますが、中長期でみれば半導体の進化に後工程は不可欠であり、すでに新たな市場が形成されつつあります。

実際にサムスンやTSMC、またラピダスもパッケージング技術の研究開発を公表しており、特にサムスンとTSMCといった海外ファウンドリー大手が、日本に研究開発拠点を開設している点も注目です。

後工程材料における日系メーカーの品質や信頼性の高さが表れているとも言えるのではないでしょうか。

2.5D 3D実装

では最後に、最新のパッケージング技術についてみていきましょう。

世界の巨大メーカーからも一目を置かれ、最前線を走る日系化学メーカーですが、最新のパッケージング技術で飛躍が見込まれる企業はどこなのでしょうか。

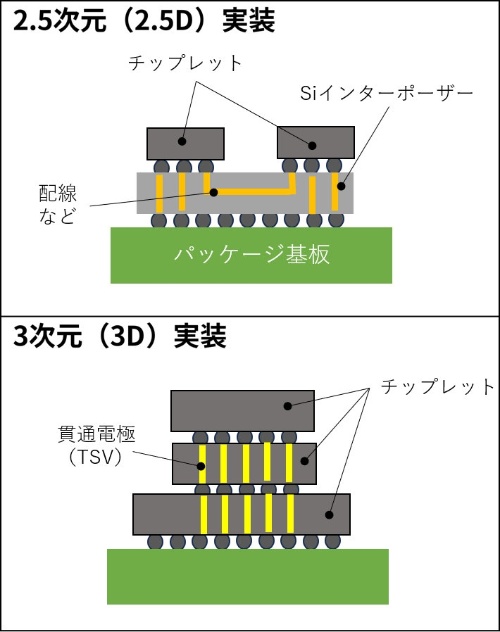

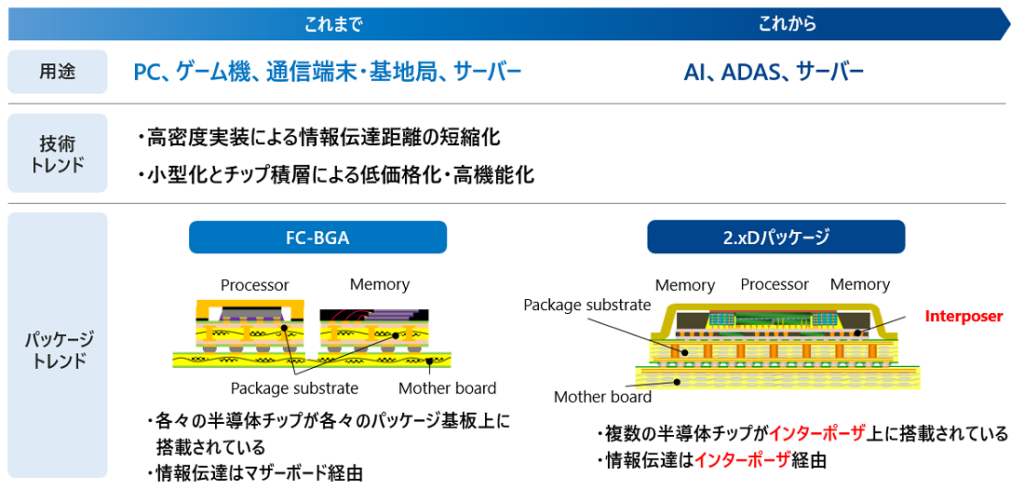

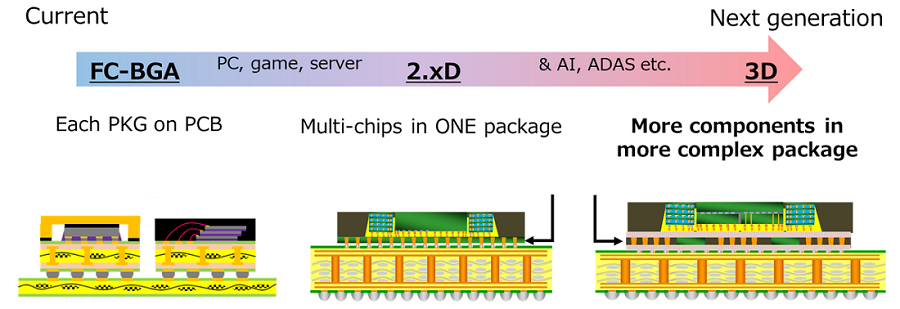

まず異なるチップを集積するチップレットの実現手段として注目されているのが、2.5Dや3D実装です。

2.5D実装

まず2.5Dから解説すると、インターポーザ―と呼ばれる基板の上に異なるチップを並べる手法で、

チップは水平方向(二次元)に並んでいますが、インターポーザ―にチップを積層しているので、2.5次元と表現されます。

インターポーザ―を介してチップ間の情報伝達が行われるため、従来のマザーボードを経由するよりチップ間の距離が短く、

信号処理のロスを小さくすることができるため、より情報伝達を高速化できるようです。

なんとなく分かったような、分からんような、といった感じですが、2.5Dはどんぶりで、インターポーザ―というご飯の上に、複数のおかず(チップ)を乗せたら効率的に食べれるよね、くらいのイメージです。

ゆえに2.5Dでは、チップの台座となるインターポーザ―が大事になってくるのですが、インターポーザ―にはシリコンウエハーに前工程技術で回路を形成したシリコン系が用いられます。

シリコンウエハーの使用量が増えるため、信越やSUMCOらはニッコリかもしれませんが、シリコン系は高いので、安価なガラスや有機インターポーザーの採用も拡大しているようです。

ガラスではAGCや大日本印刷、有機インターポーザ―では再配線層を利用したものが有望とされ、再配線層では旭化成らが手掛けていますが、レゾナックも液状やフィルム状を提案しているようです。

また信越化学はインターポーザ―を用いない基板製造装置と新工法を開発しており、各社の戦略には着目ですね。

3D実装

続いて3D実装について。これは言葉そのままで、チップを3次元に実装していきます。

垂直方向にチップレットを積層するので、2.5Dよりも高価ですが高密度に集積でき、配線の長さもさらに短くなるので、消費電力の削減や高速信号伝送などにも有利とみられています。

2.5Dではご飯(インターポーザ―)の上におかず(チップ)をいくつか乗せていましたが、3Dではチップをチップの上に縦に重ね、貫通電極で貫くので、焼き鳥みたいな感じですね。

3D実装ではチップ同士の接合方法が重要になり、ハイブリッドボンディングと呼ばれる技術に注目されています。

またチップにチップを重ねるため、製造工程用テープのパーティクルがチップ上残ると接続不良の原因となるなど、製造プロセスに求められる技術水準は大きく上がっていくものと考えられますね。

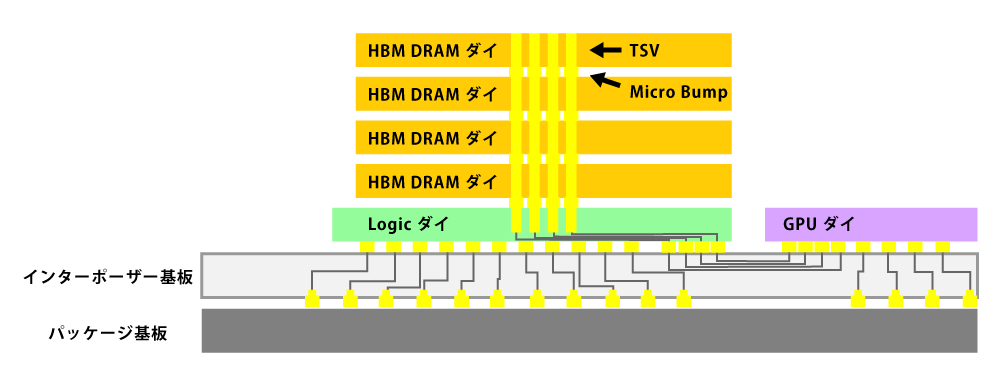

また生成AI向けの半導体にも三次元実装技術は用いられるため、続いて解説していきます。

AI半導体

最後に生成AIに用いられる半導体について触れておきます。

生成AIではメモリーの容量や速度が重要になるため、メモリーにはDRAMを3D実装した最先端のHBMというものが用いられます。

加えてこうしたメモリー半導体とロジック半導体の高度な連携が必要になることから、シリコンインターポーザ―に1ロジックと6メモリを乗せる、TSMCの2.5Dパッケージが採用されているようです。

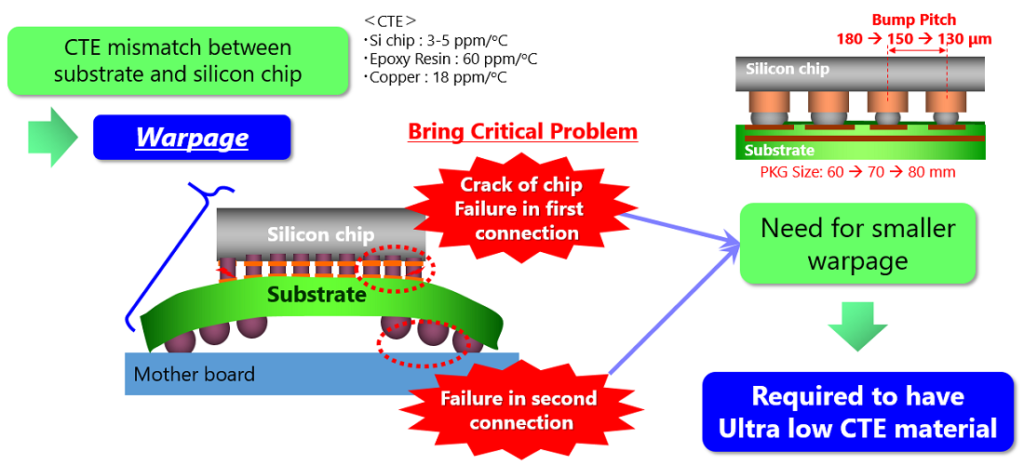

パッケージング技術の粋が集まっていますが、いろいろ詰め込むためにパッケージは大型化しており、こうなると反りや発熱対応などが課題となるため、材料に求められる要求も指数関数的に増加しています。

AI半導体に関して、後工程大手のレゾナックはTIMやNCFといった材料を提供するだけでなく、

次世代パッケージのコンソーシアムを設立するなど、企業間の連携も進めています。

後工程ではいろいろな材料が使われているため、企業間のすり合わせも重要になるわけですね。